# Advanced Packaging Technologies usher in a new era in the semiconductor marketplace

David Skellern david.skellern@mq.edu.au

#### Take aways from this talk

- Advanced packaging technologies will re-enable widespread use of custom semiconductor designs in products worldwide

- S3B is influencing the positioning and growth of semiconductor activities in Australia

- Building and operating advanced packaging plants in Australia

+ Gaining access to semiconductor global supply chain companies

will make us competitive in mainstream semiconductor and other markets

#### **CAD** Licenses

## Training and Fundamental Research

High license costs and accessibility compared to Europe, North America and Taiwan

Major change for academic licenses following discussions with Cadence:

US Style university program rolled out across country Substantial discounts for teaching and fundamental research purposes

#### Start-ups

Facilitated introductions between start ups and vendors Begun discussions with CAD vendors around start-up programs Idea is to host a pool of licenses accessible to start-ups – promising discussions ongoing

## "

## The number of transistors on a microchip doubles every two years.

- Gordon E Moore

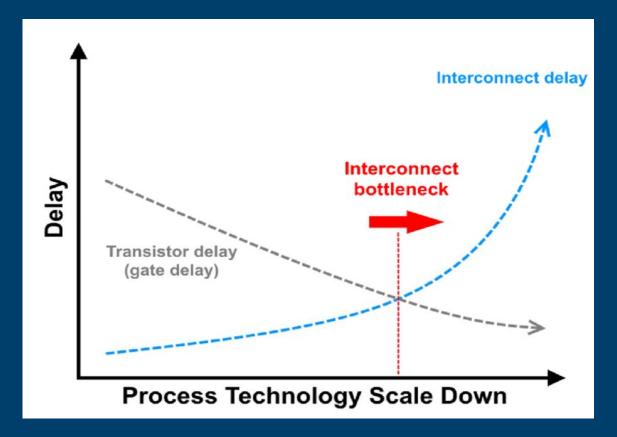

#### Effective End of Moore's Law - Its All About The Wire

3DInCities

### 3nm Lithography – Jensen Huang – Nvidia CEO

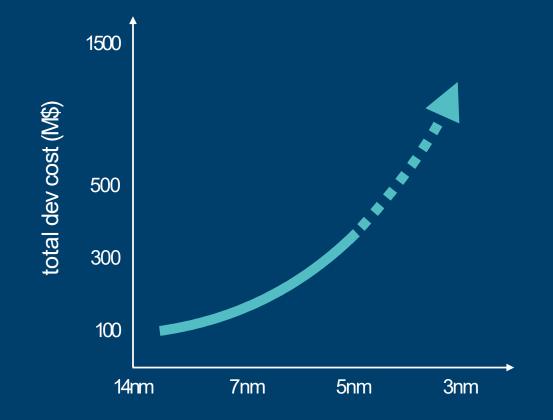

### Soaring cost of chip design

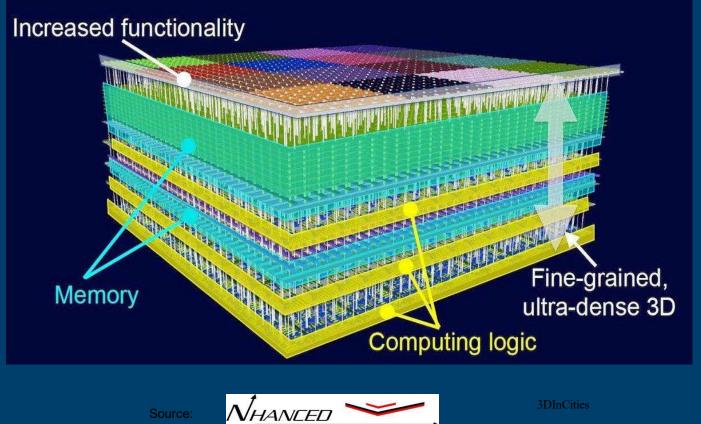

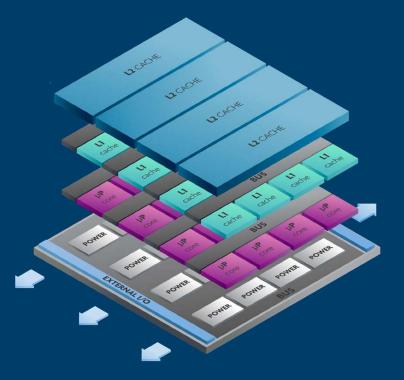

#### 3D packaging - dramatically reduces wire lengths

- 95% of the power

- 98% of the delay

EMICONDUCTORS

## "

It may prove to be more economical to also build large systems out of smaller functions, which are separately packaged and interconnected.

- Gordon E Moore

#### Bob Patti Vision of the Future - Foundry 2.0

A new semiconductor industry paradigm is evolving... A Finishing Foundry that takes the standardized building blocks from traditional semiconductor manufacturers and uses advanced packaging and additive manufacturing to create highly customized components with superior performance targeting small and medium sized markets.

(Essentially a semi fab without front-end-of-line)

### **AP Elements: Bonding**

Millimeters → Microns

Kilograms ➡ Grams

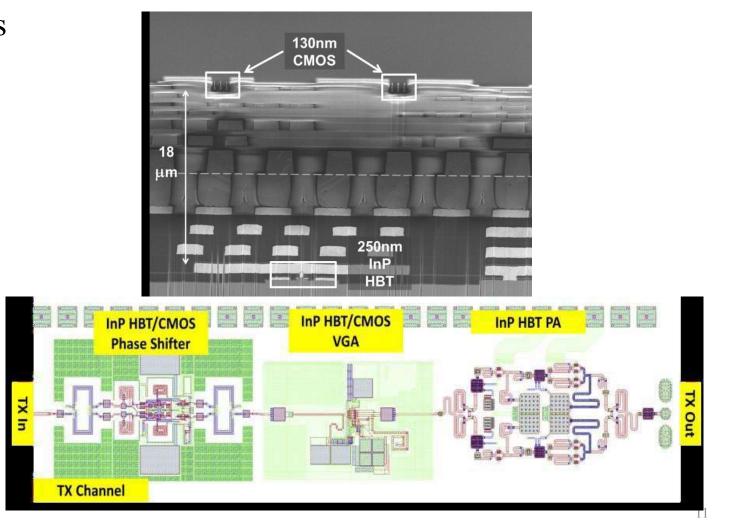

Mixed Materials Best of Class

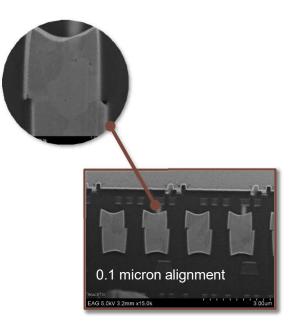

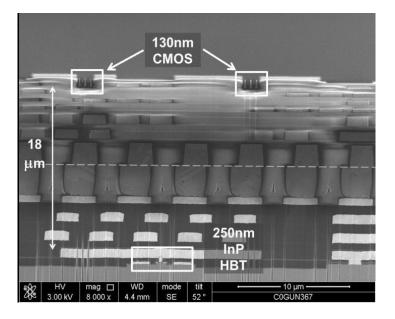

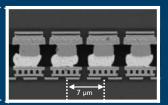

#### A Powerful New Tool: Hybrid Bonding – One of Many

Millimeters → Microns

Kilograms i Grams

Global Foundries top wafer

Teledyne InP bottom wafer

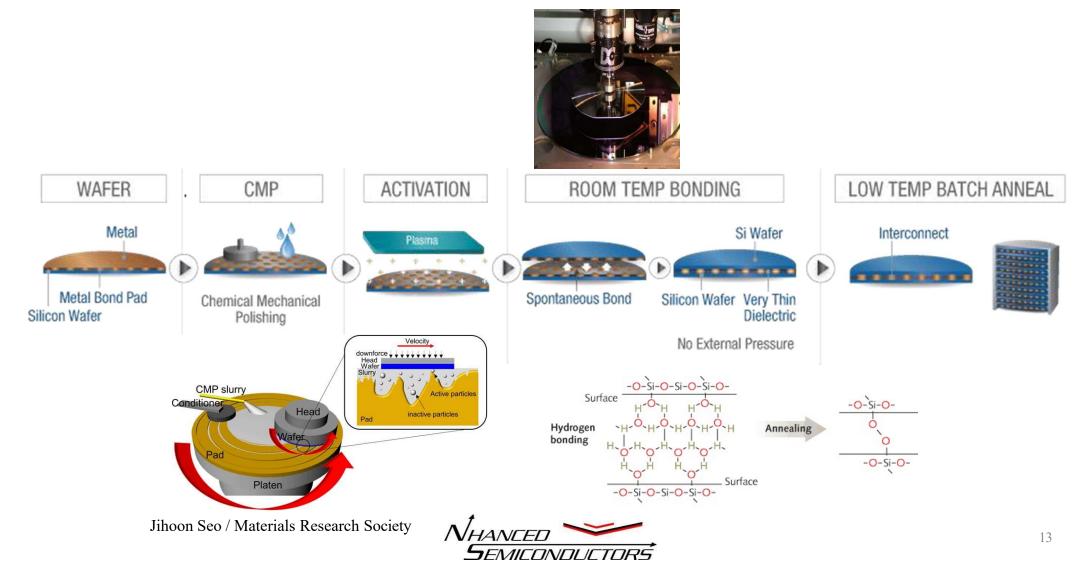

#### DBI®: Low Temperature Hybrid Bonding Process

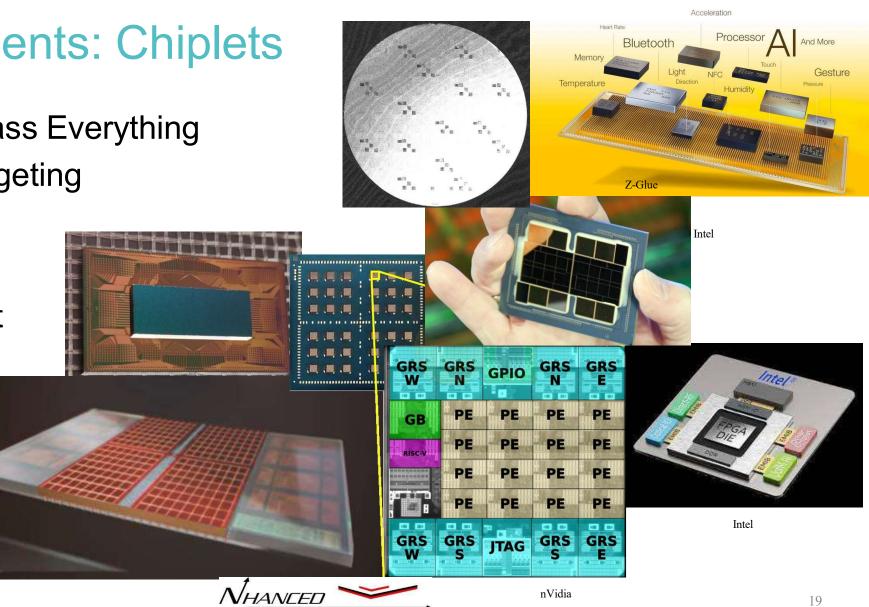

## **AP Elements: Chiplets**

- **Best of Class Everything** •

- Easy retargeting

- Lower risk •

- **IP** reuse •

- Lower cost •

AMD

SEMICONDUCTORS

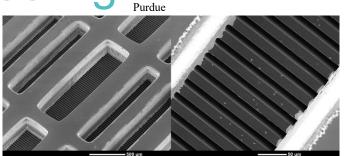

### **AP Elements: Microfluidics and Cooling**

#### Chip Scale Cooling For Ultra-Dense Electronics

#### Packaging advances to enable Integration of ever-increasing Functionality

| Ponte Vecchio, HPC                                                                                                        | Blurring the boundary between<br>wafer & package                                     |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|--|

| <ul> <li>Nodes</li> <li>MIB &amp; Foveros</li> <li>Transistors</li> <li>MiB &amp; Foveros</li> <li>Transistors</li> </ul> | Transient thermal optimization for Performance per Watt gain                         |  |  |  |

| Industry Record for Integration                                                                                           | Industry leading Thermal-Power-<br>Performance Modeling from<br>Transistor to System |  |  |  |

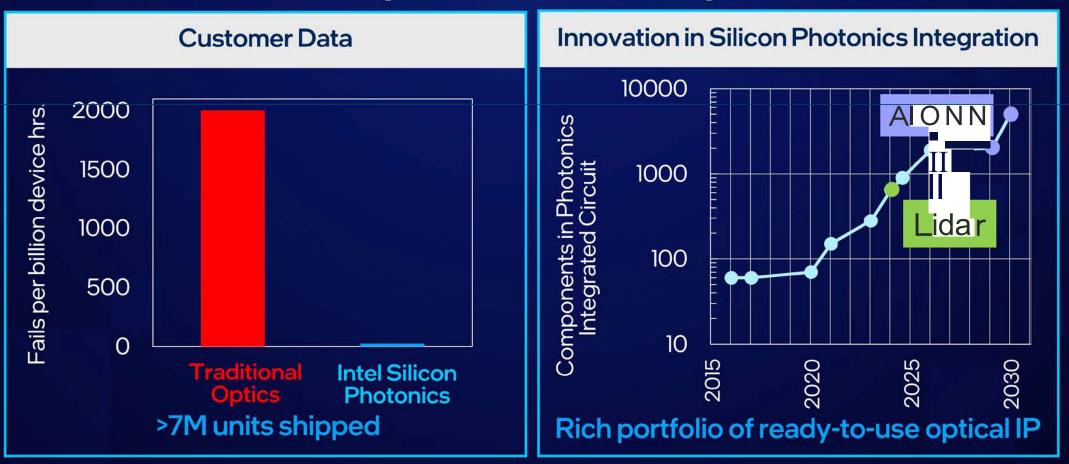

#### Integration of Silicon Photonics improves Reliability

A. Kelleher, IRPS 2023 keynote

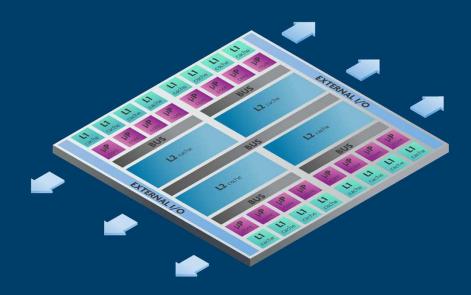

#### The need for a more aggressive semiconductor & compute systems roadmap

#### How will we realize this exponential increase?

#### 3D stacking provides linear complexity increase

3D stacking provides linear complexity increase 2D scaling provides exponential complexity increase

## Potential roadmap extension

| N7                     | N5                                                               | N3     | N2        | A14       | A10       | A7                            | A5        | A3          | A2     |  |

|------------------------|------------------------------------------------------------------|--------|-----------|-----------|-----------|-------------------------------|-----------|-------------|--------|--|

|                        |                                                                  |        |           |           |           | Continued dimensional scaling |           |             |        |  |

| Metal Pitch 40<br>[nm] | 28                                                               | 22     | 21        | 18        | 16        | 16-14                         | 16-12     | 16-12       | 16-12  |  |

| Metal Tracks 7         | Device and material innovatio<br>Metal Tracks 7 6 6 6 5 5 5 4 <4 |        |           |           |           | vations<br><4                 |           |             |        |  |

| m                      | П                                                                | m      | E         | E         |           | E                             | B         | B           |        |  |

| FinFET                 | Finfet                                                           | Finfet | GAA       | GAA       | GAA       | GAA                           | CFET      | CFET        | CFET   |  |

|                        |                                                                  |        | Nanosheet | Nanosheet | Forksheet | Forksheet                     | Context-a | ware interc | Atomic |  |

|                        |                                                                  |        |           |           |           |                               |           |             |        |  |

|                        |                                                                  |        |           |           |           |                               |           |             |        |  |

|                        |                                                                  |        |           |           |           |                               |           |             |        |  |

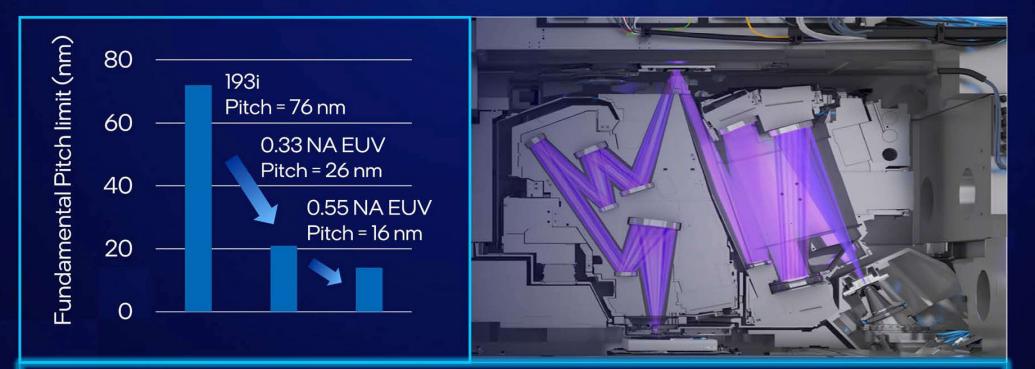

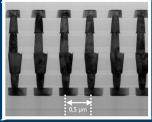

#### High-NA EUV improves resolution to enable further Silicon Technology Scaling

Intel in partnership with ASML will be the first to bring high-NA EUV to high volume manufacturing

Image from ASML

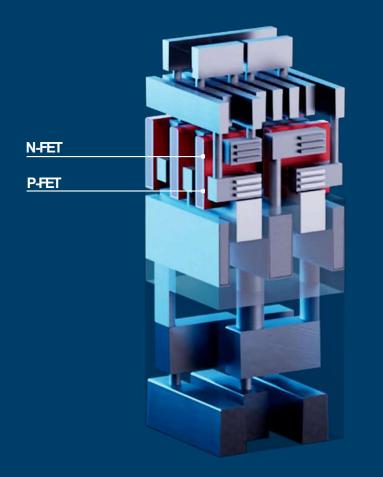

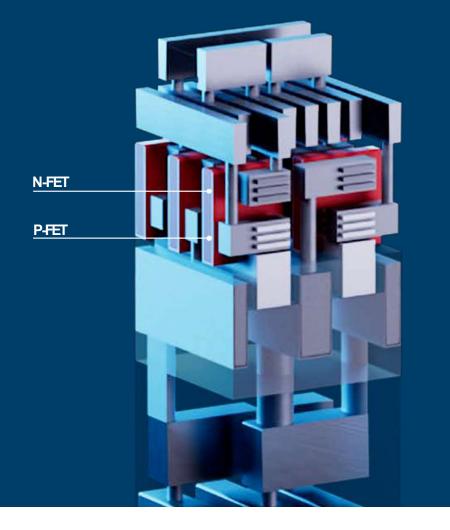

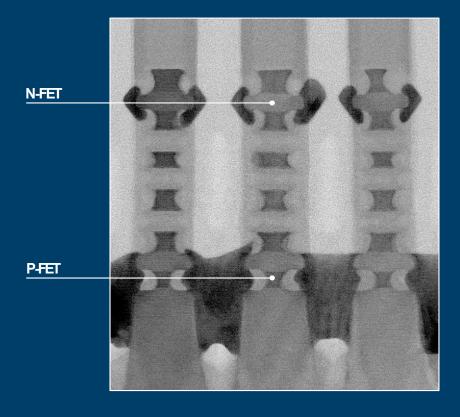

## Complementary FET (CFET)

## Complementary FET (CFET)

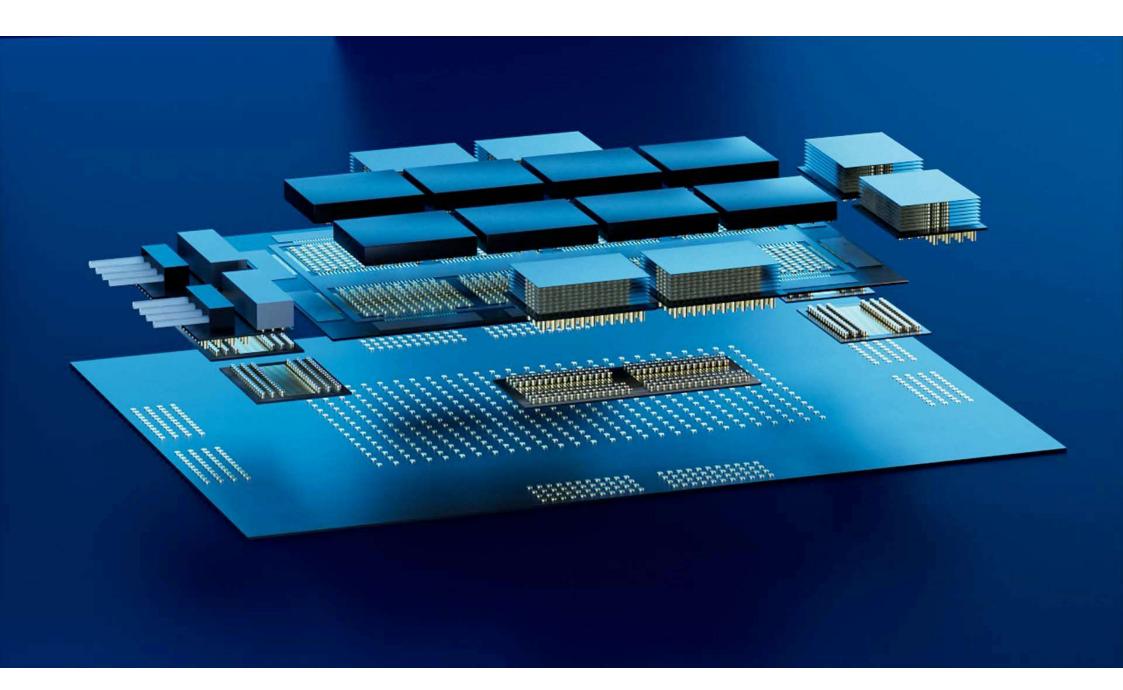

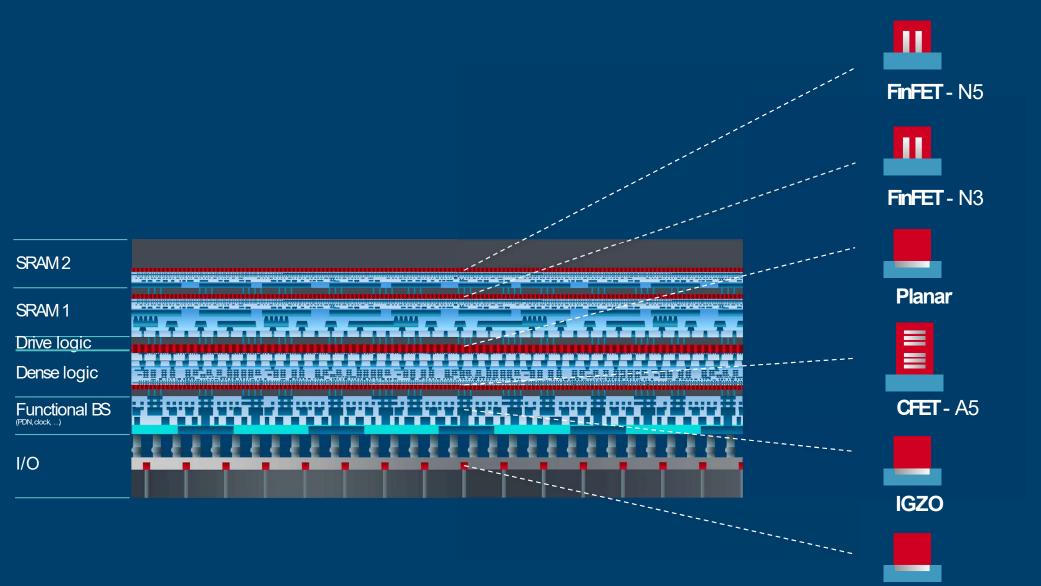

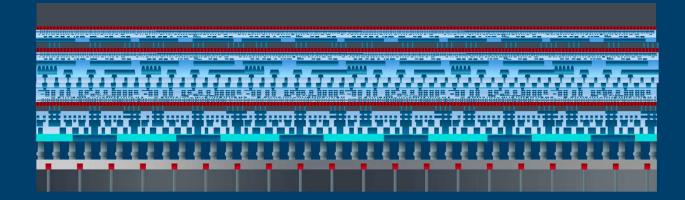

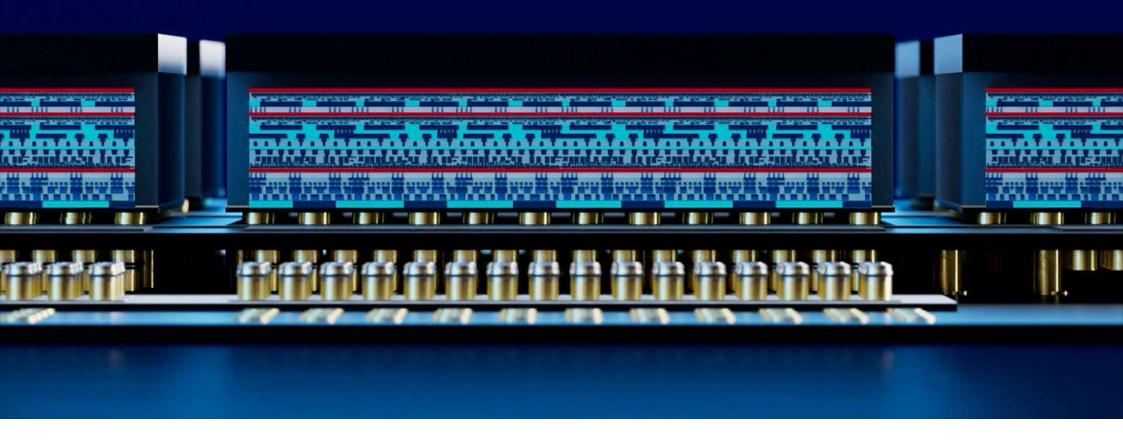

### We need to combine a multitude of approaches

| SRAM 2        |  |

|---------------|--|

| SRAM 1        |  |

| Drive logic   |  |

| Dense logic   |  |

| Functional BS |  |

| I/O           |  |

| SRAM 2        |  |

|---------------|--|

| SRAM 1        |  |

| Drive logic   |  |

| Dense logic   |  |

| Functional BS |  |

| I/O           |  |

Cu-Cu Hybrid Bonding

Back-side Power Distribution

D2W using micro-bump

| SRAM 2        | A A A A A A A A A A A A A A A A A A A |

|---------------|---------------------------------------|

|               |                                       |

| SRAM 1        |                                       |

| Drive logic   |                                       |

| Dense logic   |                                       |

| Functional BS |                                       |

| I/O           |                                       |

|               |                                       |

**Planar** - N28-N14

#### Potential roadmap extension

|           | 2018                          | 2020  | 2022  | 2024                    | 2026                    | 2028                    | 2030                    | 2032         | 2034         | 2036                  |

|-----------|-------------------------------|-------|-------|-------------------------|-------------------------|-------------------------|-------------------------|--------------|--------------|-----------------------|

|           | N7                            | N5    | N3    | N2                      | A14                     | A10                     | <b>A</b> 7              | A5           | A3           | <b>A</b> 2            |

|           |                               |       |       |                         |                         |                         |                         |              |              |                       |

|           | Continued dimensional scaling |       |       |                         |                         |                         |                         |              | l scaling    |                       |

|           |                               |       |       |                         |                         |                         |                         |              |              |                       |

| Metal p   | nm] <b>40</b>                 | 28    | 22    | 21                      | 18                      | 16                      | 16-14                   | 16-12        | 16-12        | 16-12                 |

|           |                               |       |       |                         |                         |                         |                         | evice and ma | atorial inno | atione                |

| Metal tra | acks 7                        | 6     | 6     | 6                       | 5                       | 5                       | 5                       | 4            |              | 4                     |

|           |                               |       |       |                         |                         | - <b>-</b>              | - <b>1</b> 1            |              |              |                       |

|           |                               |       |       |                         |                         |                         | E                       |              |              |                       |

|           |                               |       |       |                         |                         |                         |                         |              |              |                       |

|           | FnFET                         | FnFET | FNFET | <b>GAA</b><br>Nanosheet | <b>GAA</b><br>Nanosheet | <b>GAA</b><br>Forksheet | <b>GAA</b><br>Forksheet | CFET         | CFET         | <b>CFET</b><br>Atomic |

|           |                               |       |       |                         |                         |                         |                         |              |              |                       |

|           |                               |       |       |                         |                         |                         |                         | Context-a    | ware interco | onnect                |

|           |                               |       |       |                         |                         |                         |                         |              |              |                       |

##

## Thank You For Being Here!